## D-TACQ Solutions

High Performance Simultaneous Data Acquisition

# Intelligent Simultaneous Analog Input

- Maximum number simultaneous channels payload

- Compact PCI standalone, peripheral and system slot card

- Standalone: card is a networked device, typically running an EPICS IOC.

- Peripheral: multiple cards under control of a system slot card, int the traditional CPCI sense. Used for specialized applications and high bandwidth streaming.

- System Slot card: the digitizer can control other peripheral mode cards, from D-TACQ or third parties. The digitizer becomes a Programmable Automation Controller.

- FPGA DSP capability.

- Standard: boxcar filtering on data stream

- Custom: digital down-converter, lock-in amplifier, complex threshold detection

- User Programmable:

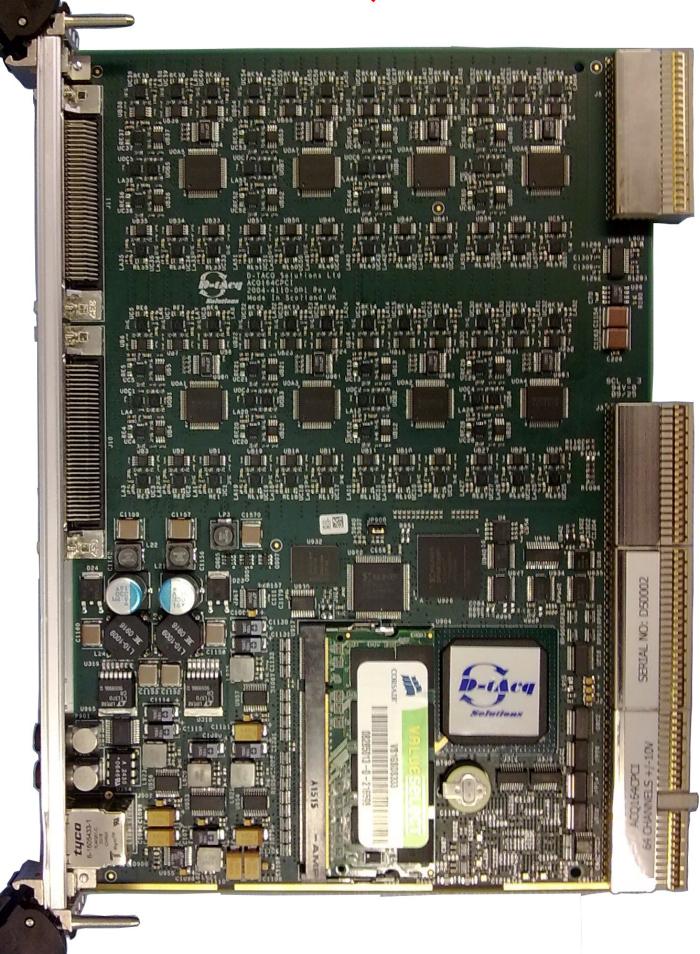

- 32 bit ARM microprocessor, runs Linux with full MMU, 1GB memory, Ethernet interfaces.

- 64 bit PCI bus for latency and sustained streaming.

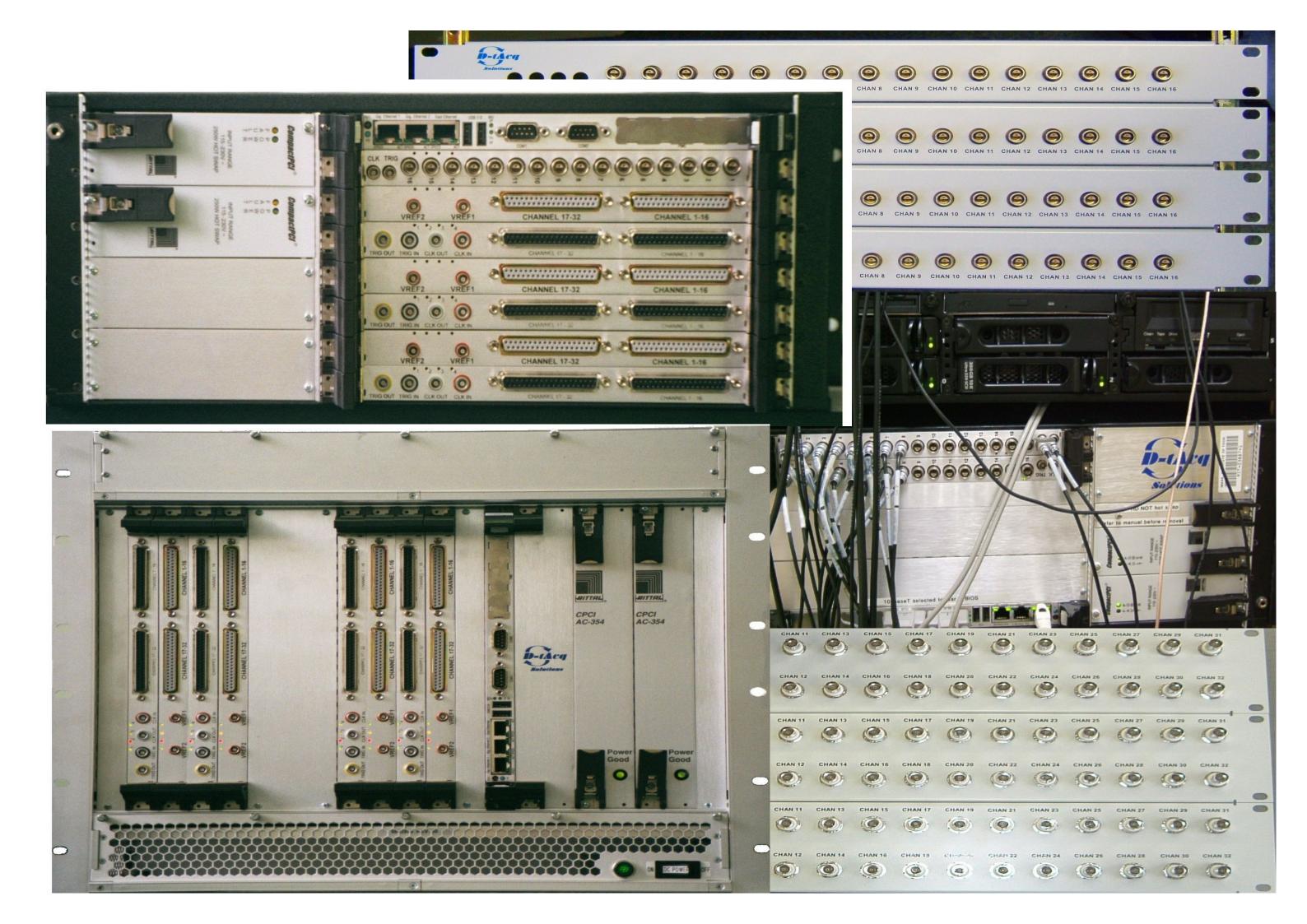

## ACQ196CPCI

#### Maximum Channels

- 96 channels x 500kS/s 16 bit differential, protected inputs.

- Optional Analog Outputs, Digital IO RTM.

- Compact PCI standalone, peripheral and system slot card

- FPGA DSP capability.

- Ethernet Transient Recorder, 1GB memory

- PCI Low latency and sustained streaming.

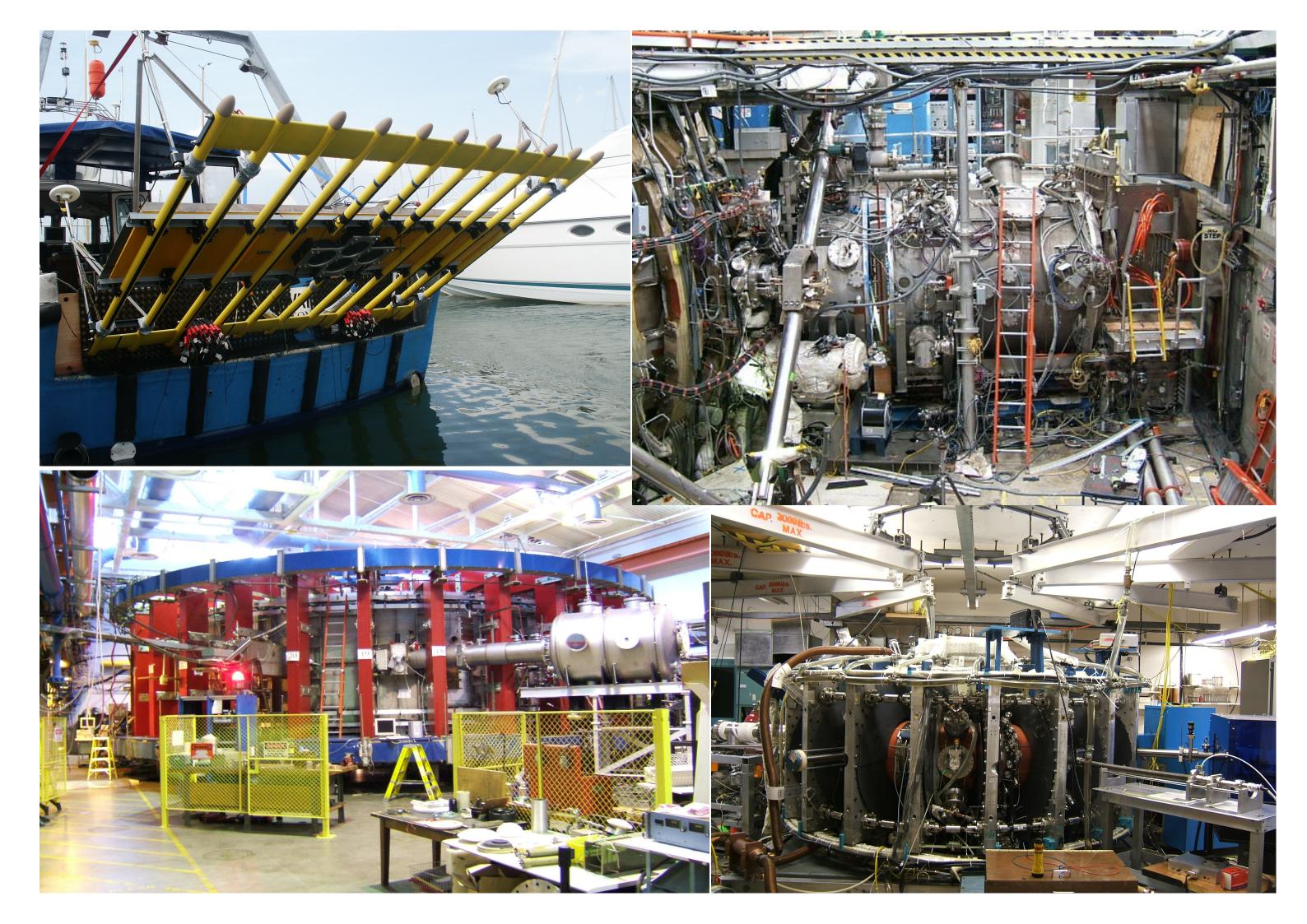

- Underwater seismic survey

- Phase array sensing

- General purpose plasma diagnostics.

- Gyrotron conditioning

- Plasma Control

- Wind tunnel testing

- Laser flashlamp condition monitoring

- Synchrotron control and monitoring

## ACQ216CPCI

#### Maximum Sample Rate

- 16 channels x 16MS/s 16 bit differential, protected inputs.

- Soft select: 12ch x 20MS/s, 8ch x 25MS/s, 4ch x 50MS/s

- Precision DDS clock option on RTM.

- Sync multiple modules to external 1MHz ref clock

- Compact PCI standalone card

- FPGA DSP capability.

- Ethernet Transient Recorder, 1GB memory.

- PCI Low latency application

- General purpose plasma diagnostics

- Klystron protection.

- Gyrotron conditioning fault monitor

- Combined Plasma Control and diagnostic.

- ATE systems.

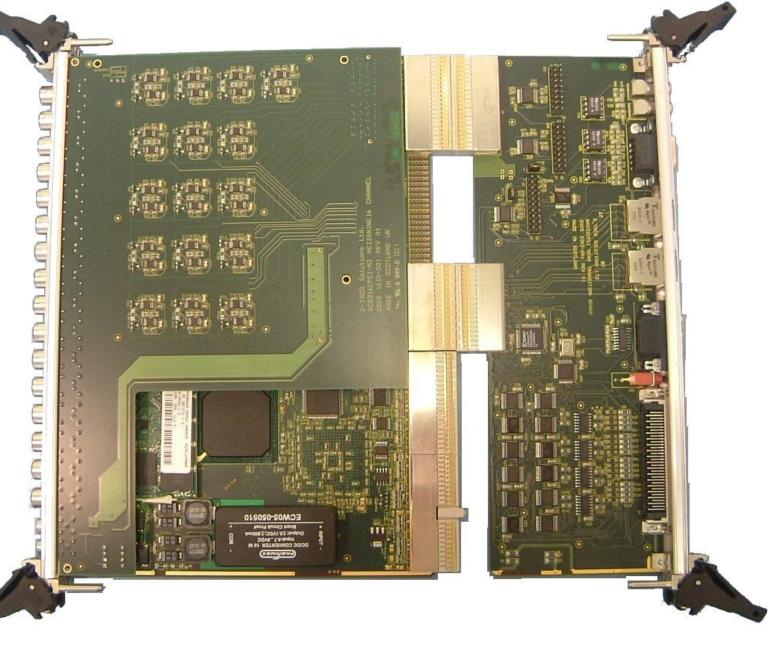

## ACQ132CPCI

#### Most channels with Mhz sampling

- 32 channels x 2MS/s *continuous* operation

- 32 channels x 65MS/s burst operation

- 14 bit differential, protected inputs

- Distributed FPGA DSP capability eg 32x oversampling FIR, 32MHz in, 2MS/s, 16 bit effective out.

- Precision clock option on-board.

- Compact PCI standalone, and system slot card

- Ethernet Transient Recorder, 1GB memory.

- High Resolution Medical Sonar

- Structural testing.

- General purpose plasma diagnostics

- RF Diagnostics

- Langmuir Probe arrays.

- Pulsed Diagnostics detectors in laser experiments.

ACQ164CPCI

**NEW Q3 2009**

High Channel Count, Very High Resolution

- 64 channels x 128kS/s continuous operation

- 24 bit resolution.

- New technology sigma delta converters, with excellent DC performance characteristic.

- 56kHz Bandwidth, brick wall filtering

- Compact PCI standalone, and system slot card

- Ethernet Transient Recorder, 1GB memory.

- Magnet power supply monitor.

- Sonar

- Structural testing.

- Precision Control Systems

- Precision Monitoring Systems

## Simultaneous Analog Output

- Maximum number simultaneous channels payload

- Compact PCI peripheral card for lowest cost.

- Simple direct register control or Arbitrary Waveform Generator AWG modes.

- 64 bits Digital Output DO.

- Both the AO and DO functions are AWG capable and may be clocked.

- Intended for use in conjunction with ACQ196/ACQ164/ACQ132 in System Slot.

- Also works with x86 host. Open Source Linux device driver provided.

## AO32CPCI

#### Low Cost Simultaneous AWG

- AO 32 channels x 1MS/s, 16 bit continuous operation

- DO 64 channels x 1MS/s continuous operation

- Simple register update mode

- Low Latency mode

- AWG modes.

- Clocked digital output.

- FPGA on board. Multi-channel PWM possible

- Compact PCI peripheral slot card

- Ideal companion card for ACQ196CPCI, ACQ132CPCI.

- AWG.

- Plasma Control System

- ATE

- Sonar Sim and Stim.

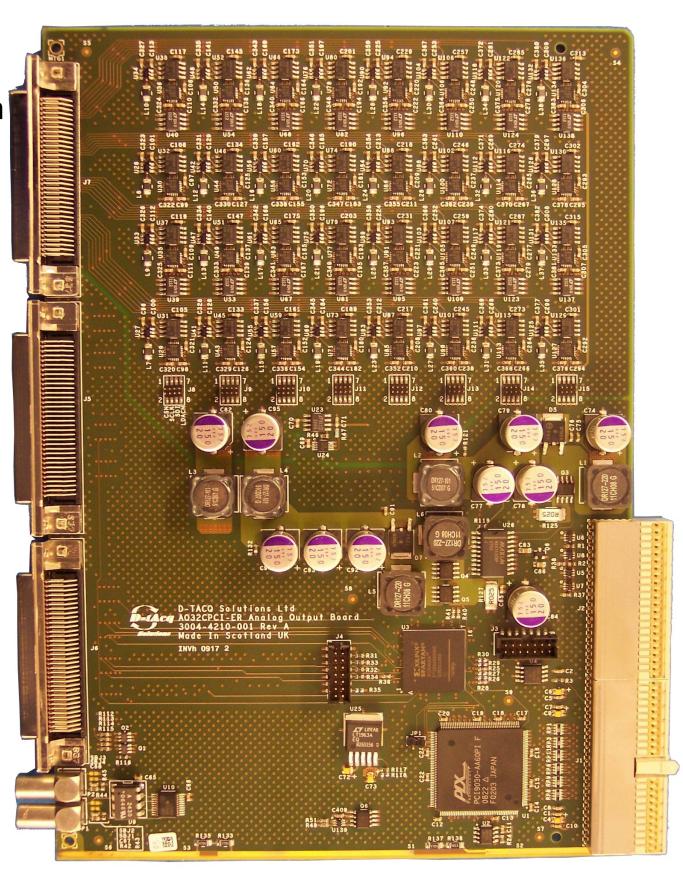

## AO32CPCI-ER

#### Simultaneous Extended Resolution AWG

- AO 32 channels x 200kS/s, 18 bit continuous operation

- DO 64 channels x 1MS/s continuous operation

- Simple register update mode

- Low Latency mode

- AWG modes.

- Clocked digital output.

- FPGA on board. Multi-channel PWM possible

- Compact PCI peripheral slot card

- Ideal companion card for ACQ164CPCI.

- Magnet power supply control.

- AWG.

- Precision control systems.

- ATE

- Sonar Sim and Stim.

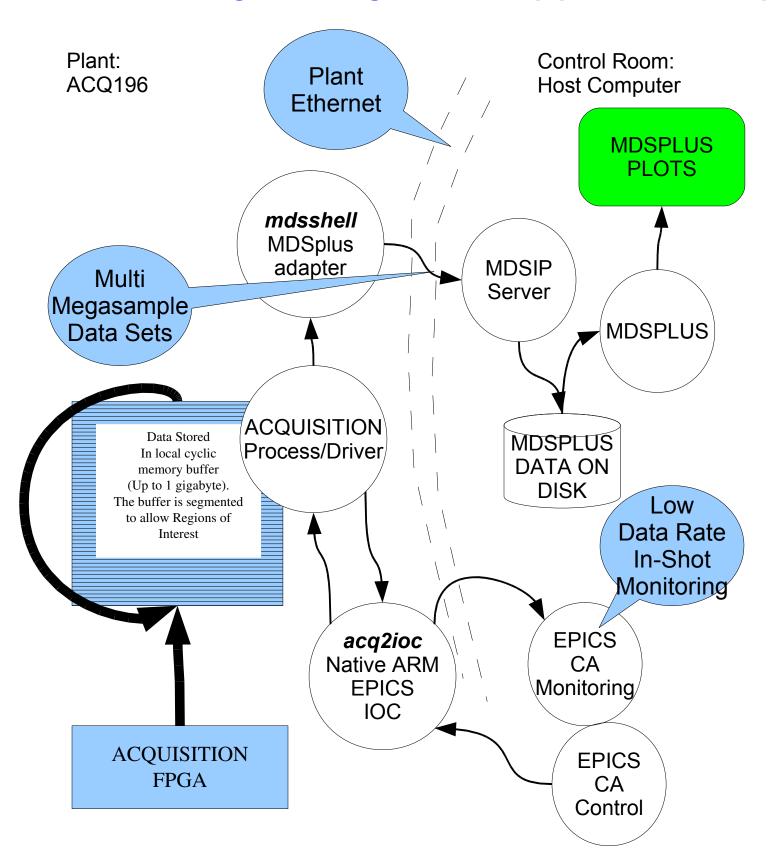

## Embedded Processor, Open Interfaces

#### Intelligent Digitizer supports MDSplus, EPICS, Webservices

- Embedded MDSplus "ThinClient" store calibrated data direct to MDS server

- [not shown] Embedded MDSIP allows MDSplus server to control digitizer. And, via the system slot function, it's possible to control other devices in the chassis.

- Embedded EPICS IOC control and mean data monitoring. Easy to add more complex sequencing on top – eg compare ratios in channels and output a trip signal.

Alternative control interface [not shown]:

- Embedded processor offers a web service interface

- SOAP RPC. Allows an external client to control every aspect of the card, or control acquisition using a high level C++ API.

- WSDL definition of the web service allows automated connection to well known WS clients – eg

MS .NET, Labview 8.20. Control possible with 5 line

VB .NET program.

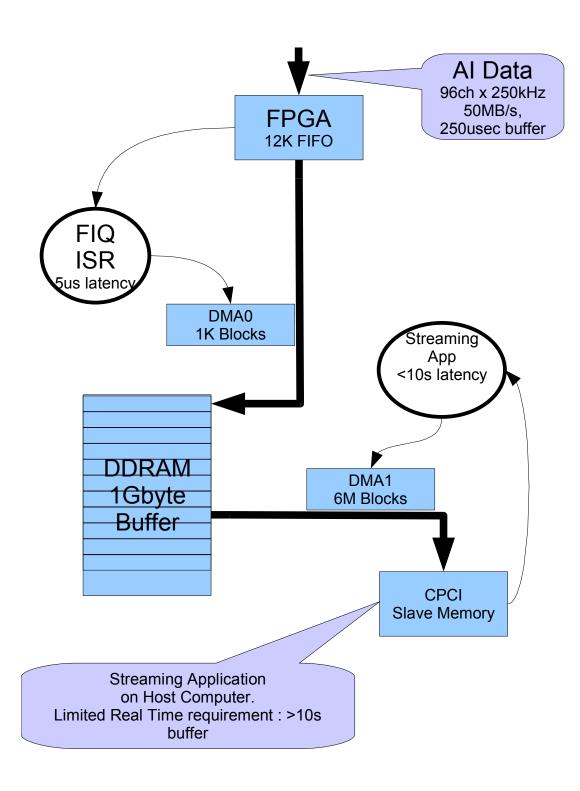

## Solutions for Long Shot/Continuous Operation

#### High Bandwidth 64bit backplane, huge buffers, intelligent DMA

- CPCI backplane operation already used extensively for PCS.

PCS applications are optimised for Latency.

- High bandwidth CPCI backplane also suitable for continuous data streaming for diagnostic applications, where the on-board DDRAM is no longer big enough to hold all the data.

- Block diagram shows firmware implementation optimised for high bandwidth. The firmware makes use of the full on-board memory (1GB) as a streaming buffer, more than 10s buffering.

- This means that the host OS has a very limited real time requirement, at least on the data acquisition side.

- Data transfer is under the control of the ACQ196, so cpu usage on the host system to handle incoming data is very low (<1% per card), leaving 99% of cpu resource free for data processing, including storage.

- Scaleable implementation eg: 4 x ACQ196, 384 channels, 250kS/s/channel, 200MB total data flow on 64bit, 33MHz backplane.

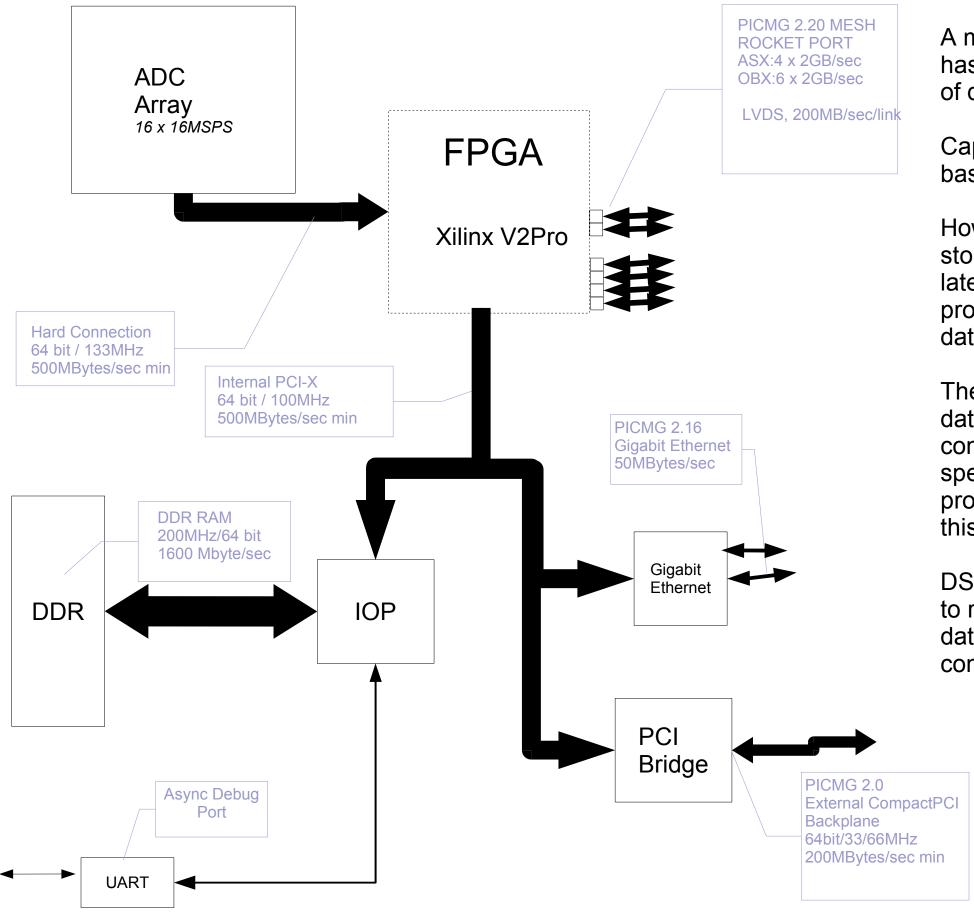

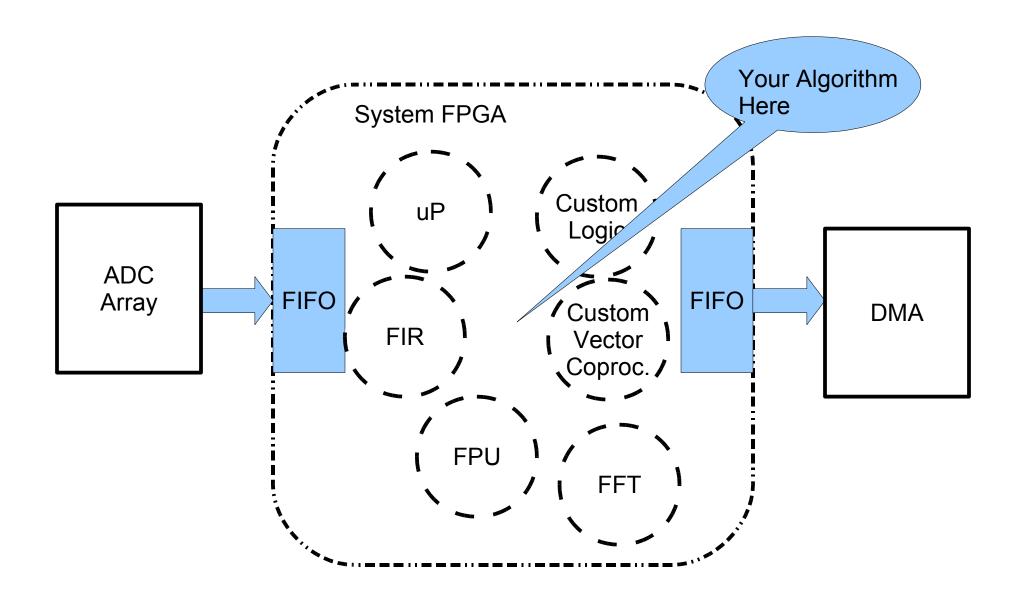

#### **ACQ216CPCI Simultaneous Digitizer Architecture**

Capture One Gigabyte Data in 2s

A modern digitizer like ACQ216CPCI has no problem capturing vast amounts of data.

Capturing and viewing raw data is a basic function of the device.

However the time to upload the data, storage of this data, and performing later analysis are all challenging problems owing to the shear volume of data.

The primary function of the FPGA is data transfer, however it can also be configured as a powerful "application specific computer". Combined with the programmable local microprocessor, this is a very flexible solution.

DSP algorithms may be applied simply to reduce data, or to make processed data available rapidly, or for real time control and protection.

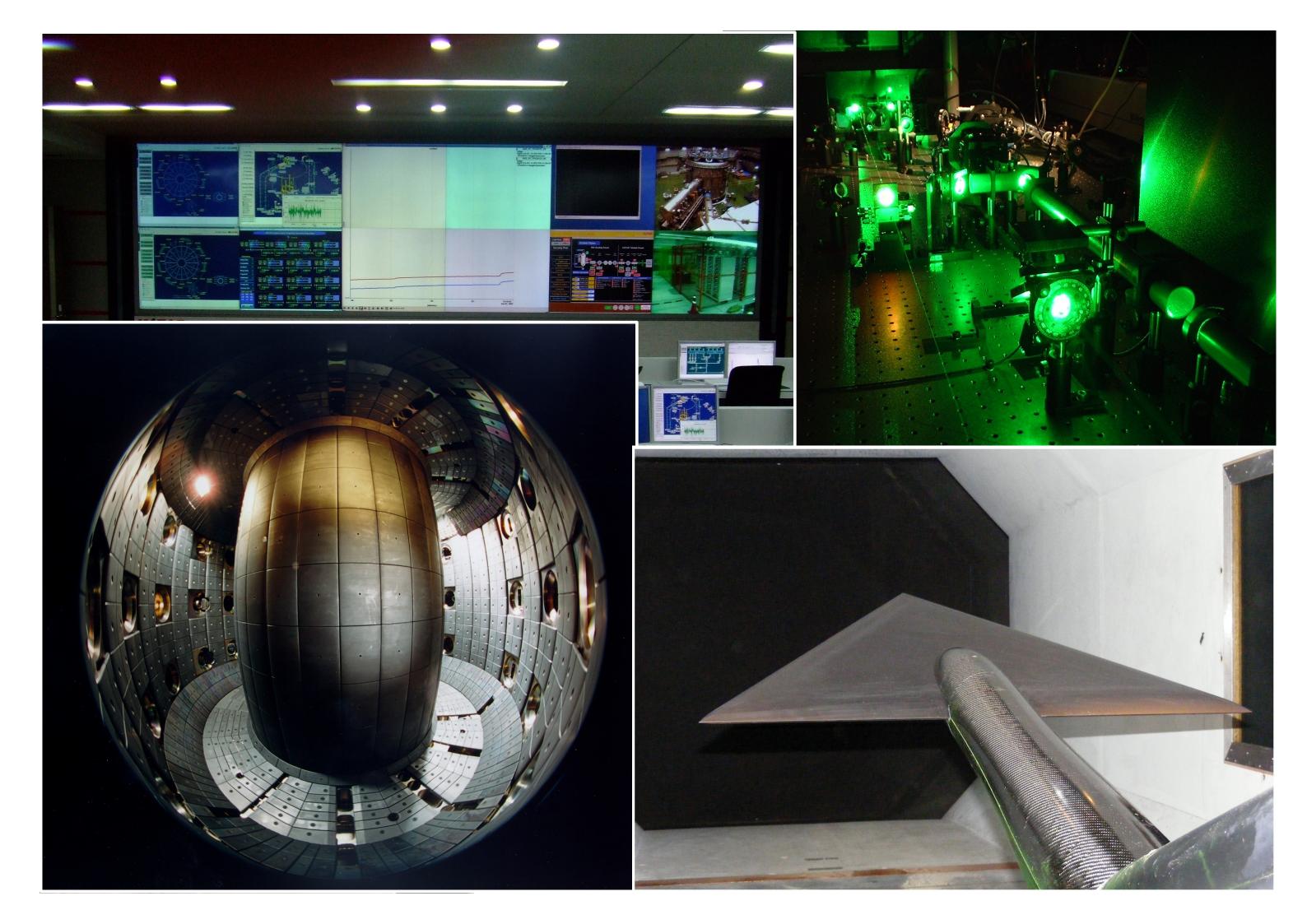

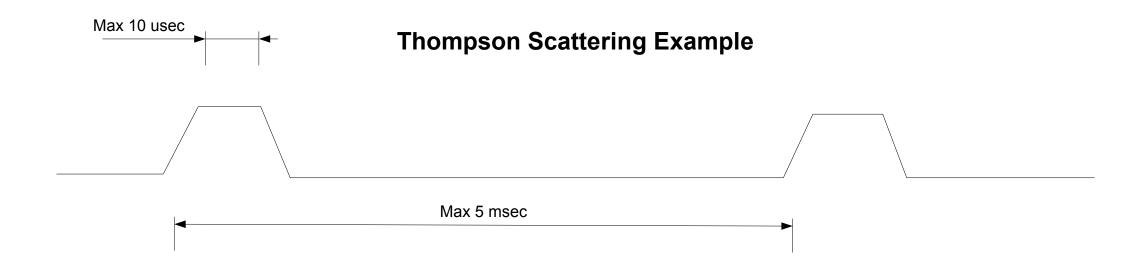

## Solutions for Thomson Scattering

#### High Channel Count, Gated Transient reduces data size

- Nearly 1400 channels, 12\*ACQ196 in one chassis

- Only interested in sampling while the laser pulse is ON, therefore use the laser pulse to gate the sampling. System only captures data during the laser pulses. This results in at least 100:1 data reduction.

- Data reduction is built into the digitizer; conserves local memory, saves network upload time and saves server storage.

- As far as the data acquisition is concerned, the pulses are random. The digitizer runs a counter on the system clock, and each pulse is stored to local memory together with a timestamp.

- After the shot, each digitizer uploads its own data set as a single large file by FTP. Host side software extracts the pulses and the timebase.

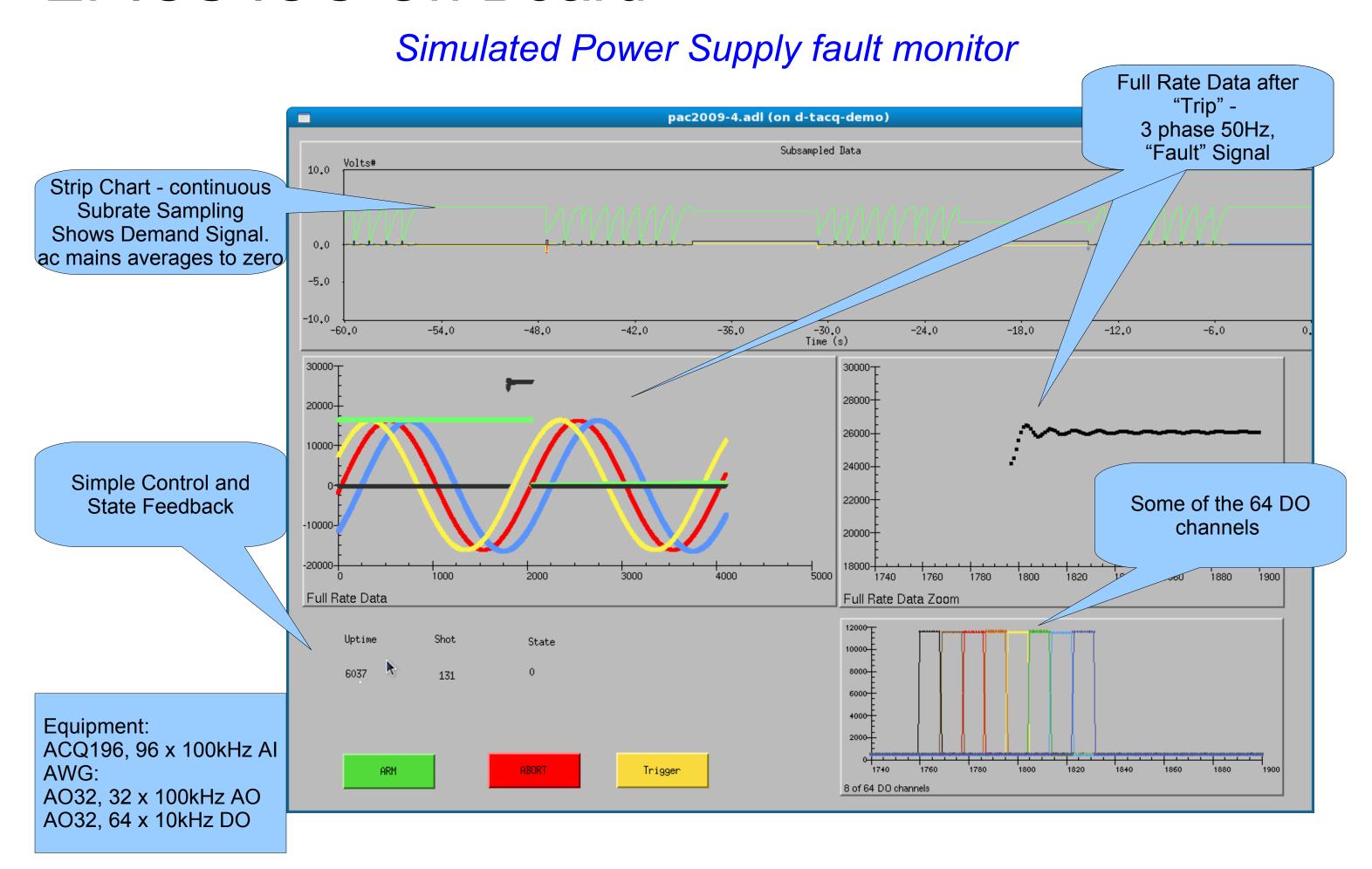

## **EPICS IOC On Board**

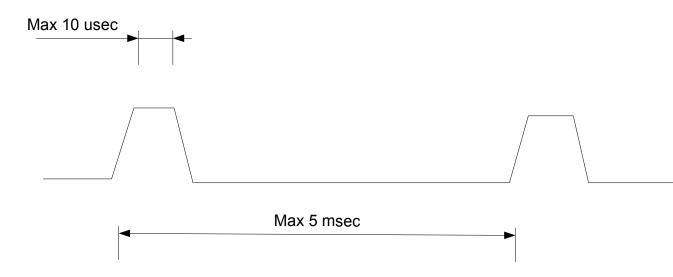

## Gated Modes: capture during Strobe

Threshold detection reduces huge data set to duration of each laser pulse.

- Several hundred capture channels, 500kS/s. Shot duration 5s, total data set > 500K bytes

- Data is only of interest during laser pulse, pulses are 10usec duration, with "random" spacing.

- Laser is rated at 400pulses per second.

- The duty cycle of the data is only 4:1000

#### Solution:

- ACQ196CPCI captures data to memory at full rate.

- Laser pulse is configured as an Event input FPGA samples, and a table of event vs approximate sample number is recorded.

- Post shot, embedded microprocessor firmware uses the event table to seed a pulse search algorithm. Each identified pulse is placed in a virtual file, ready for upload to data archive system. Data transfer by FTP or embedded MDSplus client.

- The Post shot search is very rapid, data is available for upload within 5s.

- The data upload size is reduced by factor 250, and each pulse is timestamped.

- The full data set is still available for cross check, if required.

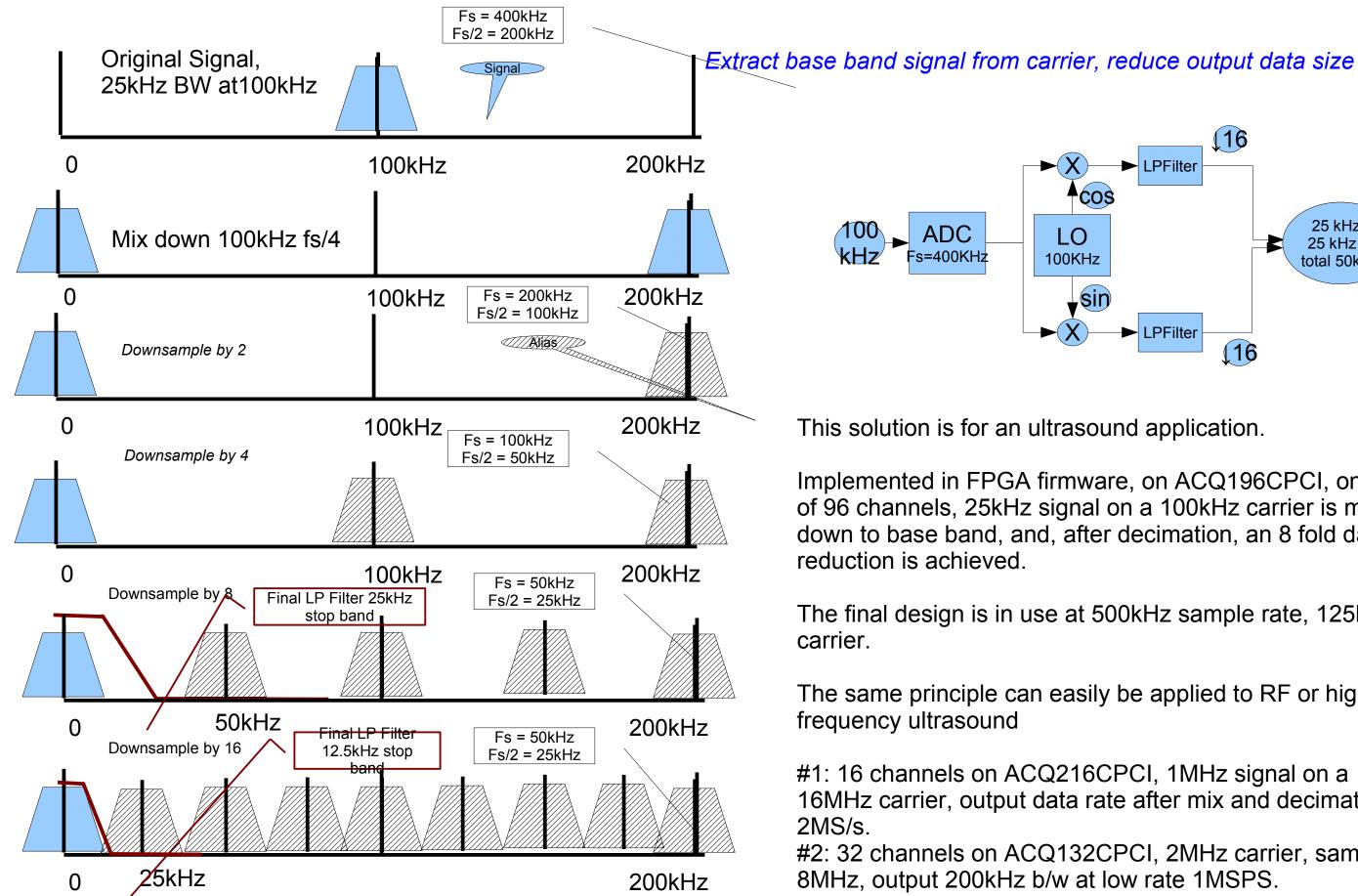

## DSP: 96 Channel Digital Down-converter

**(16**) ► LPFilter 25 kHz l **ADC** LO 25 kHz Q 100KHz total 50kHz

sin

LPFilter

116

This solution is for an ultrasound application.

Implemented in FPGA firmware, on ACQ196CPCI, on each of 96 channels, 25kHz signal on a 100kHz carrier is mixed down to base band, and, after decimation, an 8 fold data reduction is achieved.

The final design is in use at 500kHz sample rate, 125kHz carrier.

The same principle can easily be applied to RF or high frequency ultrasound

#1: 16 channels on ACQ216CPCI, 1MHz signal on a 16MHz carrier, output data rate after mix and decimation is 2MS/s.

#2: 32 channels on ACQ132CPCI, 2MHz carrier, sample at 8MHz, output 200kHz b/w at low rate 1MSPS.

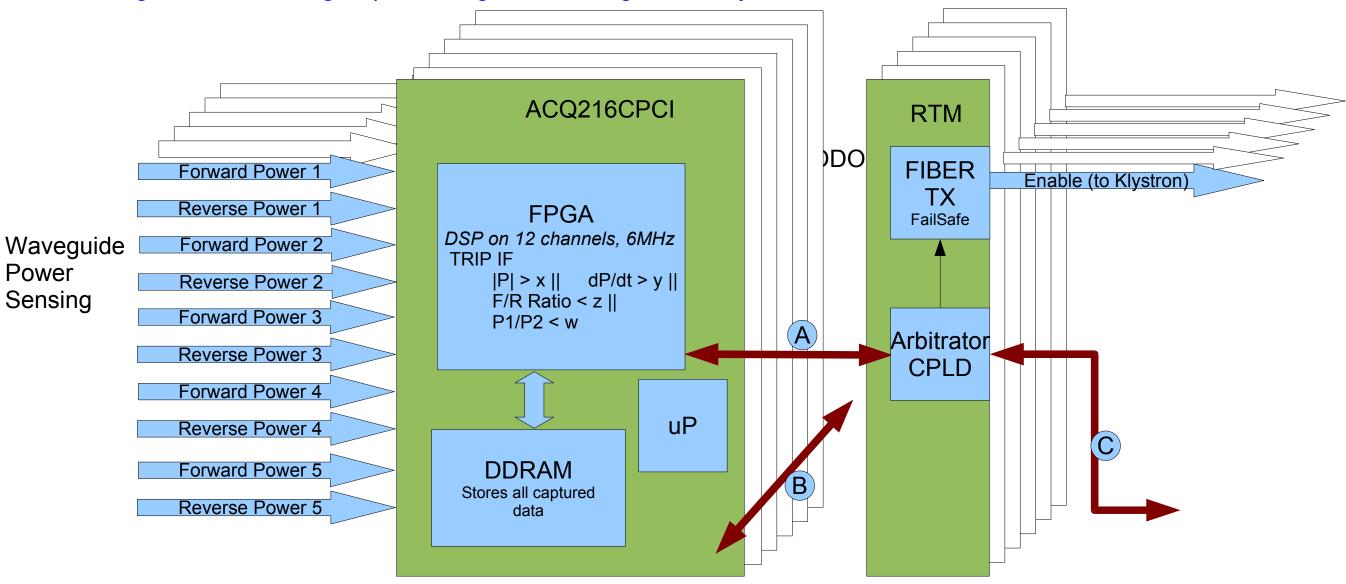

## DSP: Coupler Protection System RF signals, real time signal processing, thresholding and safety interlock.

Tokamak Microwave Heating System comprises 12 Klystrons and a "jungle gym" waveguide power delivery mechanism.

For each Klystron, Forward and Reverse Power is measured at 5 points in the waveguide.

The Protection System monitors the signals, performing absolute and ratiometric measurements against stored thresholds to generate a trip signal.

The protection system comprises 12 ACQ216CPCI digitizers, 6 in each of two 8 slot Compact PCI crates.

Each Klystron is managed by an ACQ216CPCI digitizer, monitoring 10 channels at 6MS/s and gating the Klystron by means of a Fiber Optic signal from a custom Rear Transition Module RTM.

The Trip and other handshake signals are shared between FPGA and CPLD (A), between devices using the PXI signaling backplane (B) and via off-crate connector (C). One device signaling a trip trips all devices simultaneously. Trip computed in less than 10usec.

All thresholds and ratios are pre-programmed before the shot, and all captured data, together with computation results, is uploaded to MDSplus after the shot. The cards are self contained devices connected by Gigabit Ethernet.

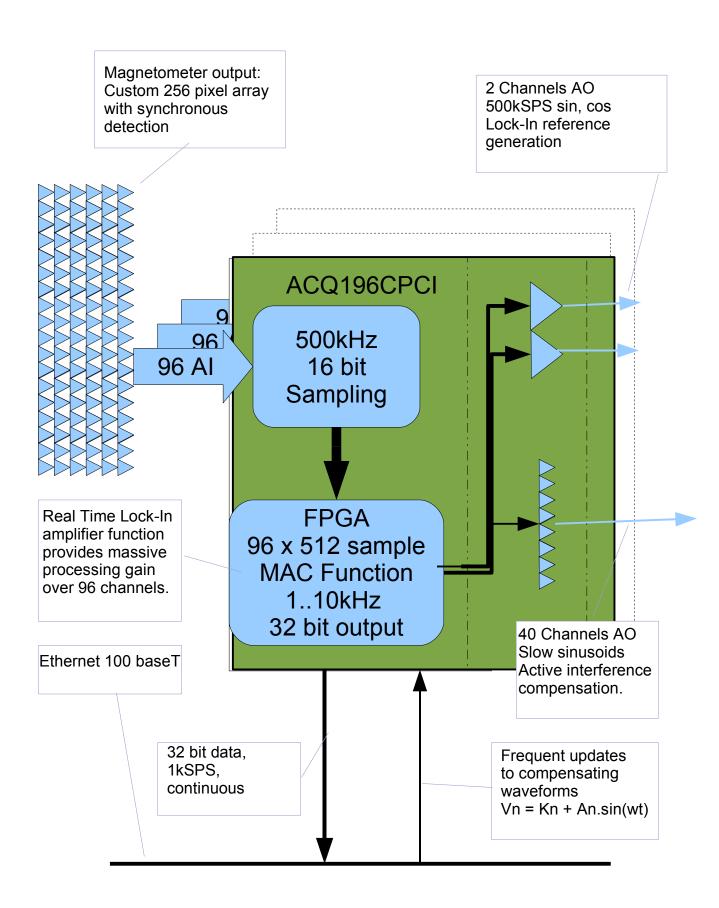

## DSP: Lock-in amplifier

#### **ACQ196CPCI Medical Imaging Application**

Continuous Streaming Data with DSP Lock In Detection

96 channel digital Lock-in amplifier provides massive SNR improvement to medical imaging application

In this case, the circuit generates its own reference signal for output to the system, but it's equally possible to pick up an external reference on an input channel.

A current fusion application for this technology records and demodulates the output of a Photo Elastic Multiplexer, in a Motional Stark Effect diagnostic.

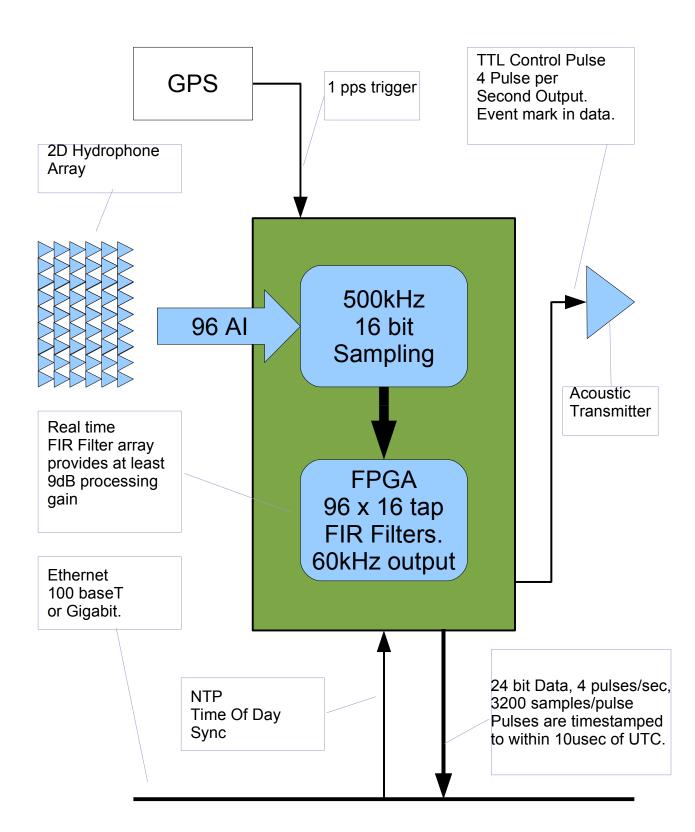

### DSP: FIR Filter

#### **ACQ196CPCI Seismic Survey Application**

Pulsed Streaming Data with Oversampling

ACQ196CPCI uses a Xilinx Spartan 3 FPGA.

Custom DSP firmware has been implemented to provide a FIR function, processing the intput data in real time, and providing a reduced-rate, decimated output.

FIR Filtering adds processing gain to Sonar application.

The FIR filter firmware can be used for noise reduction in any appropriate application.

## User-Programmable Custom DSP

Software manages Data flow, Hardware co-processors transform the data.

- Possibility to instantiate an embedded microprocessor core in the FPGA.

- The core has fast, low latency access to data.

- What can you do with a 100MIPS core?. Well, first the data is presented in cache, second there is the possibility to connect the data to a dedicated math accelerator unit eg a hardware FFT function or a vector FPU.. and it's possible to have more than one embedded core.

- The vendor supplies the co-processors.

- Expected applications include threshold detection, alarms, and control.

- Implement your algorithm in C using GNU tools ...

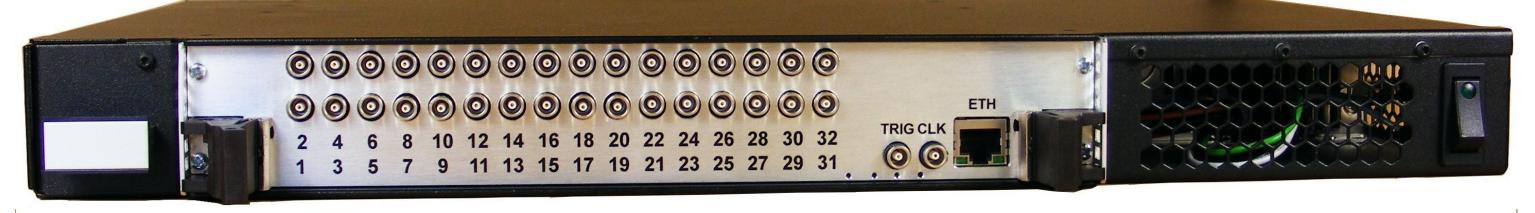

## Portable Systems 96 channels, SMA Termination, 2U Flight Case

www.d-tacq.com